Schieberegister 1

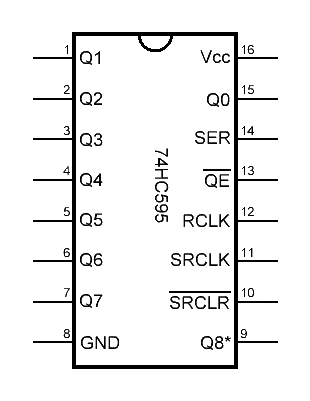

Die SN74HC595-Bausteine enthalten einen seriellen 8-Bit-Eingang und ein Parallel-Out-Schieberegister, welches einen 8-Bit-D-Typ Speicherregister speist. Das Speicherregister hat parallel 3- stufige Ausgänge. Für beide sind getrennte Takte, für das Schiebe- und Speicherregister, vorgesehen. Das Schieberegister hat ein direkt überschreibenden Löscheingang (SRCLR). Einen seriell (SER) Eingang und serielle Ausgänge zur Kaskadierung. Wenn der Output-Enable (OE)-Eingang HIGH ist, sind die Ausgänge in den hochohmigen Zustand geschaltet.

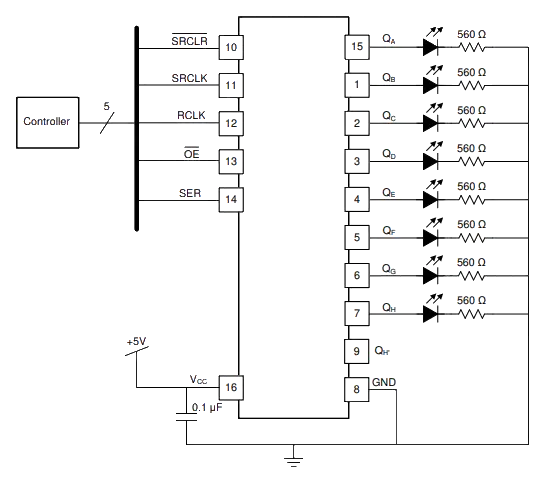

Mit dem Schieberegister lassen sich bis zu 8 Pins gleichzeitig ansteuern, wobei aber nur 3 Pins auf der Seite des Mikrocontrollers benötigt werden. Durch Verwendung von mehreren Schieberegistern können noch weitaus mehr Pins angesteuert werden.

Ein Schieberegister besteht genau genommen aus zwei Registern: das Schieberegister, in welches der Zustand der einzelnen Ausgangspins seriell, also Bit für Bit, geschoben wird. Und das Ausgangsregister, in das der Zustand des Schieberegisters auf ein Signal vom Mikrocontroller hin kopiert wird. Erst dann wird der Zustand der ins Schieberegister geschickten Daten an den Ausgangspins sichtbar.

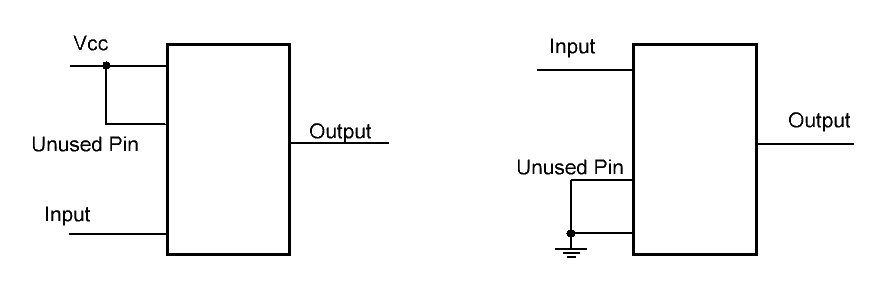

In vielen Fällen werden Funktionen oder Teile von Funktionen digitaler Logikbausteine nicht genutzt. Beispielsweise, wenn nur zwei Eingänge eines UND-Gatters mit drei Eingängen verwendet werden oder nur 3 der 4 Puffergatter. Solche Eingangspins sollten nicht unbeschaltet bleiben, da die undefinierten Spannungen, an den Ausgängen, zu nicht definierten Zuständen führen.

Das nebenstehende Bild legt die Regeln fest, die unbedingt eingehalten werden müssen. Alle unbenutzten Eingänge von digitalen Logikbausteine müssen an eine hohe oder niedrige Vorspannung angeschlossen werden, um undefinierte Zustände zu verhindern. Die Logikebene, sollte auf einen bestimmten, unbenutzten Eingang angewendet werden. Das hängt von der Funktion des Geräts ab. In der Regel werden sie an GND oder VCC angeschlossen.

Funktionsablauf

Über GND und VCC erfolgt die Spannungsversorgung. GND wird mit Masse verbunden, VCC mit +5V oder +3,3V.

Mit OE wird die Ausgabe des Schieberegisters generell aktiviert. Dieser Eingang wird daher mit GND verbunden.

Die Dateneingabe erfolgt über SER, RCLK und SRCLK in folgender Reihenfolge:

1.) SRCLK auf 0 setzen.

2.) RCLK auf 0 setzen.

3.) SER auf 0 oder 1 setzen, je nach dem, welche Information man übergeben will.

4.) RCLK auf 1 setzen – damit der Registerinhalt um ein Bit verschoben und das Bit von SER in das Register übernommen.

5.) Schritt 2-4 für die übrigen sieben Bits wiederholen.

6.) SRCLK auf 1 setzen – damit werden die geschriebenen Bits zu den Ausgängen übernommen.